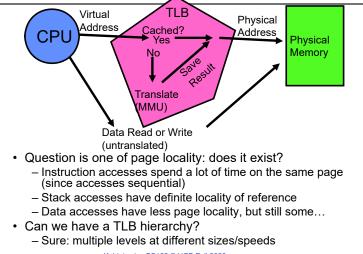

### Recall: Caching Applied to Address Translation

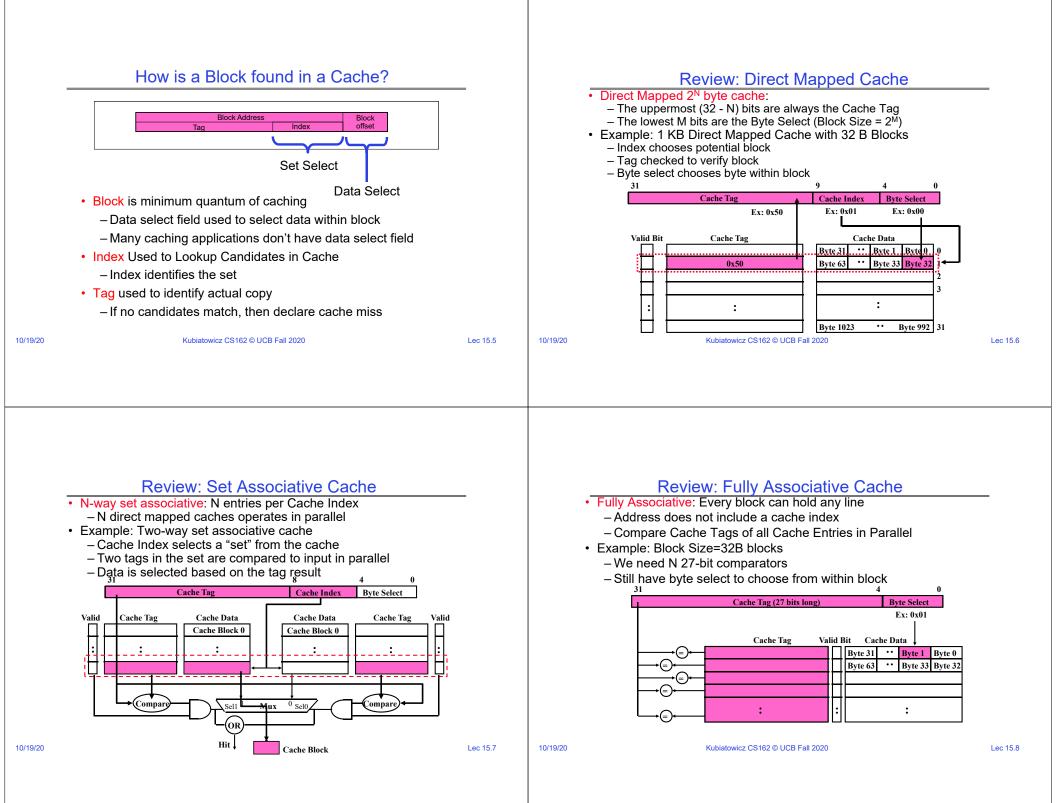

## Recall: A Summary on Sources of Cache Misses

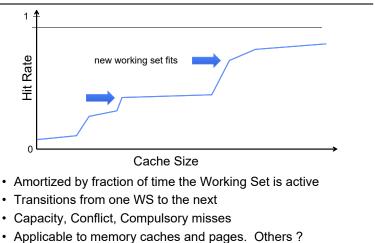

- · Compulsory (cold start or process migration, first reference): first access to a block

- "Cold" fact of life: not a whole lot you can do about it

- Note: If you are going to run "billions" of instruction, Compulsory Misses are insignificant

- Capacity:

- Cache cannot contain all blocks access by the program

- Solution: increase cache size

- Conflict (collision):

- Multiple memory locations mapped to the same cache location

- Solution 1: increase cache size

- Solution 2: increase associativity

- Coherence (Invalidation): other process (e.g., I/O) updates memory

10/19/20

Kubiatowicz CS162 © UCB Fall 2020

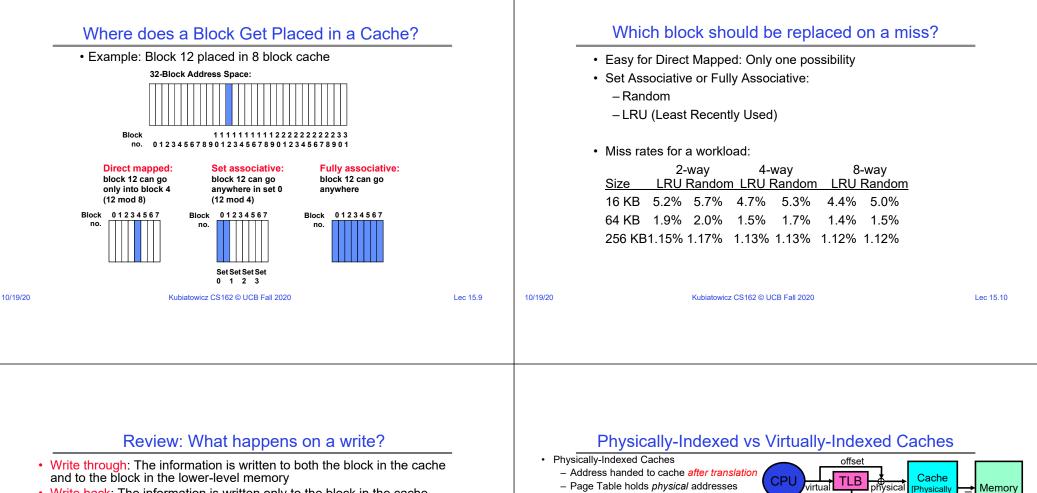

- Write back: The information is written only to the block in the cache

- Modified cache block is written to main memory only when it is replaced

- Question is block clean or dirty?

- Pros and Cons of each?

- -WT:

- » PRO: read misses cannot result in writes

- » CON: Processor held up on writes unless writes buffered

- -WB:

- » PRO: repeated writes not sent to DRAM processor not held up on writes

- » CON: More complex

- Read miss may require writeback of dirty data

Kubiatowicz CS162 © UCB Fall 2020

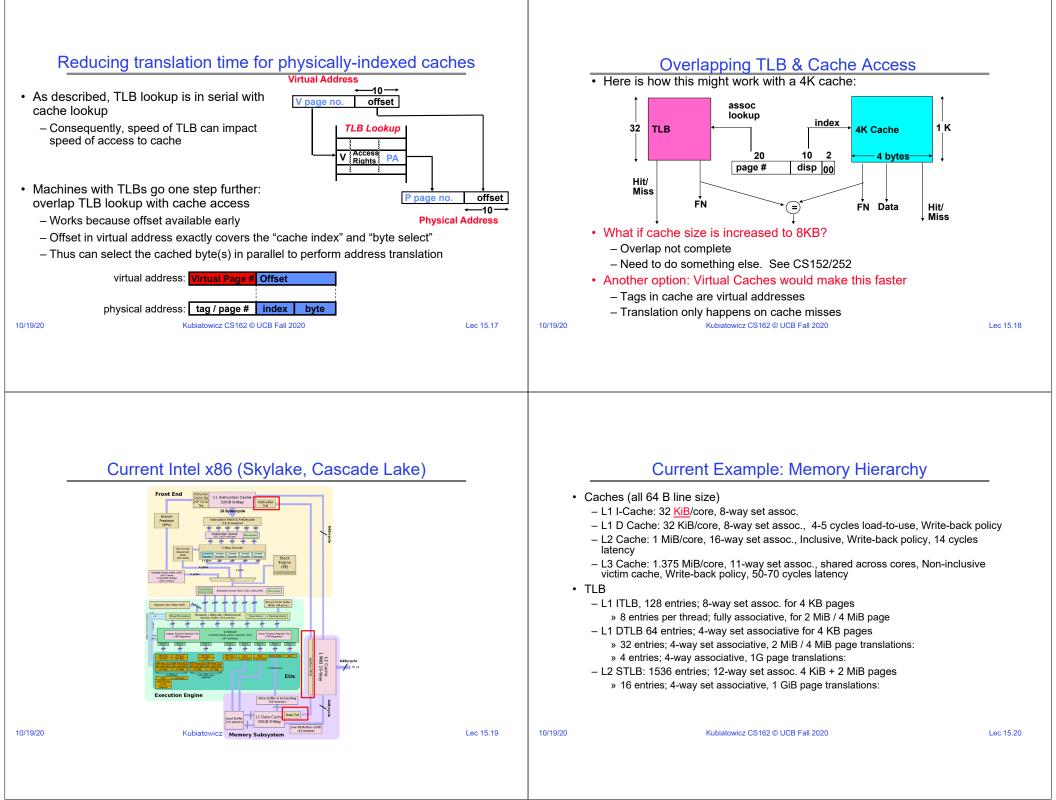

- Benefits:

- » Every piece of data has single place in cache

- » Cache can stay unchanged on context switch

- Challenges:

- » TLB is in critical path of lookup!

- Pretty Common today (e.g. x86 processors)

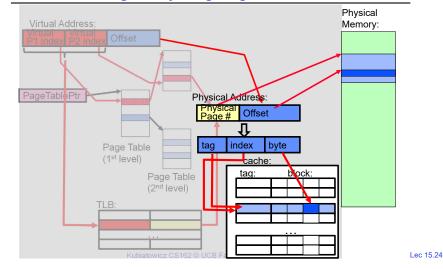

- Virtually-Indexed Caches

- Address handed to cache before translation

- Page Table holds *virtual* addresses (one option)

- Benefits:

- » TLB not in critical path of lookup, so can be faster

- Challenges:

- » Same data could be mapped in multiple places of cache » May need to flush cache on context switch

Kubiatowicz CS162 © UCB Fall 2020

We will stick with Physically Addressed Caches for now!

Lec 15.11

Lec 15.12

fd

Memory

physical,

indexed

Cache

Virtually

indexed

offset

TLB

[Virtually

addressed]

Page Table

physical

irtua

virtua

virtual

[Physically

addressed]

Page Table

| <ul> <li>Administrivia</li> <li>Midterm 2: Coming up on Thursday 10/29 <ul> <li>Topics: up until Lecture 17: Scheduling, Deadlock, Address Translation, Virtual Memory, Caching, TLBs, Demand Paging, I/O</li> <li>Will REQUIRE you to have your zoom proctoring setup working <ul> <li>You must have screen sharing, audio, and your camera working</li> <li>Make sure to get your setup debugged and ready!</li> </ul> </li> <li>Review Session: 10/27 <ul> <li>Details TBA</li> </ul> </li> <li>Kubi Office Hours: M/W 2:00-3:00 <ul> <li>Let me know if this doesn't work</li> </ul> </li> <li>US Election coming up: Don't forget to Vote! <ul> <li>Voting is one of the most important things you can do if you are allowed</li> <li>Don't miss the opportunity!</li> </ul> </li> </ul></li></ul> |  | <ul> <li>What TLB Organization Makes Sense?</li> <li>What TLB Organization Makes Sense?</li> <li>Wether the sense of the s</li></ul> |          |                                                                                                                                                                                                                                                                                                                                      |           |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|

| – Don't miss the op<br>– Be safe, of cours                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  | Lec 15.13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10/19/20 | <ul> <li>What if use low order bits of page as index into TLB?</li> <li>» First page of code, data, stack may map to same entry</li> <li>» Need 3-way associativity at least?</li> <li>– What if use high order bits as index?</li> <li>» TLB mostly unused for small programs</li> <li>Kubiatowicz CS162 © UCB Fall 2020</li> </ul> | Lec 15.14 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |                                                                                                                                                                                                                                                                                                                                      |           |  |

## TLB organization: include protection

- How big does TLB actually have to be?

- -Usually small: 128-512 entries (larger now)

- -Not very big, can support higher associativity

- · Small TLBs usually organized as fully-associative cache

- -Lookup is by Virtual Address

- -Returns Physical Address + other info

- What happens when fully-associative is too slow?

- -Put a small (4-16 entry) direct-mapped cache in front -Called a "TLB Slice"

- Example for MIPS R3000:

| Virtual Address | Physical Address | Dirty | Ref | Valid | Access | ASID |

|-----------------|------------------|-------|-----|-------|--------|------|

| 0xFA00          | 0x0003           | Y     | N   | Y     | R/W    | 34   |

| 0x0040          | 0x0010           | N     | Y   | Y     | R      | 0    |

| 0x0041          | 0x0011           | N     | Y   | Y     | R      | 0    |

|                 |                  |       |     |       |        |      |

# Example: R3000 pipeline includes TLB "stages"

| MIPS R3000 Pipeline |                |          |           |         |           |  |

|---------------------|----------------|----------|-----------|---------|-----------|--|

|                     | Inst Fetch     | Dcd/ Reg | ALU / E.A | Memory  | Write Reg |  |

|                     | TLB I-Cache RF |          | Operation |         | WB        |  |

|                     |                |          | E.A. TLB  | D-Cache |           |  |

TLB

64 entry, on-chip, fully associative, software TLB fault handler

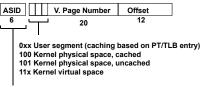

Virtual Address Space

Allows context switching among 64 user processes without TLB flush

Kubiatowicz CS162 © UCB Fall 2020

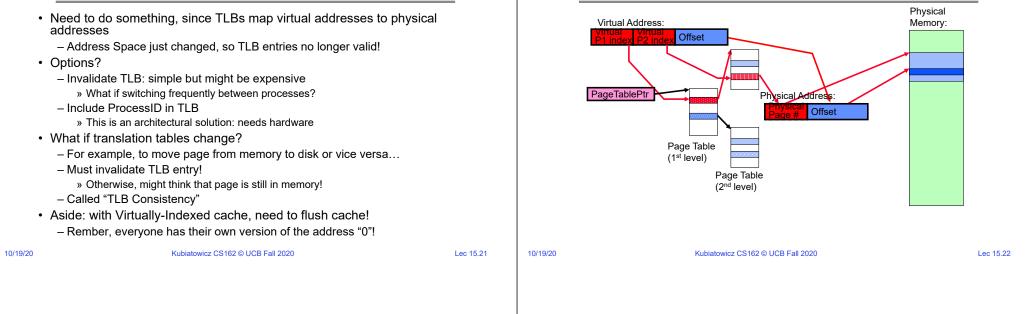

## What happens on a Context Switch?

10/19/20

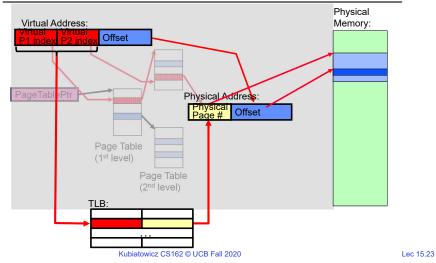

## Putting Everything Together: TLB

10/19/20

Putting Everything Together: Cache

Putting Everything Together: Address Translation

- Definitely write-back - need dirty bit!

scheduler

10/19/20

Lec 15.27

| -        | Very Different Situation Toda     | y         | _        | <text><code-block></code-block></text> |           |

|----------|-----------------------------------|-----------|----------|----------------------------------------|-----------|

| 10/19/20 | Kubiatowicz CS162 © UCB Fall 2020 | Lec 15.33 | 10/19/20 | Kubiatowicz CS162 © UCB Fall 2020      | Lec 15.34 |

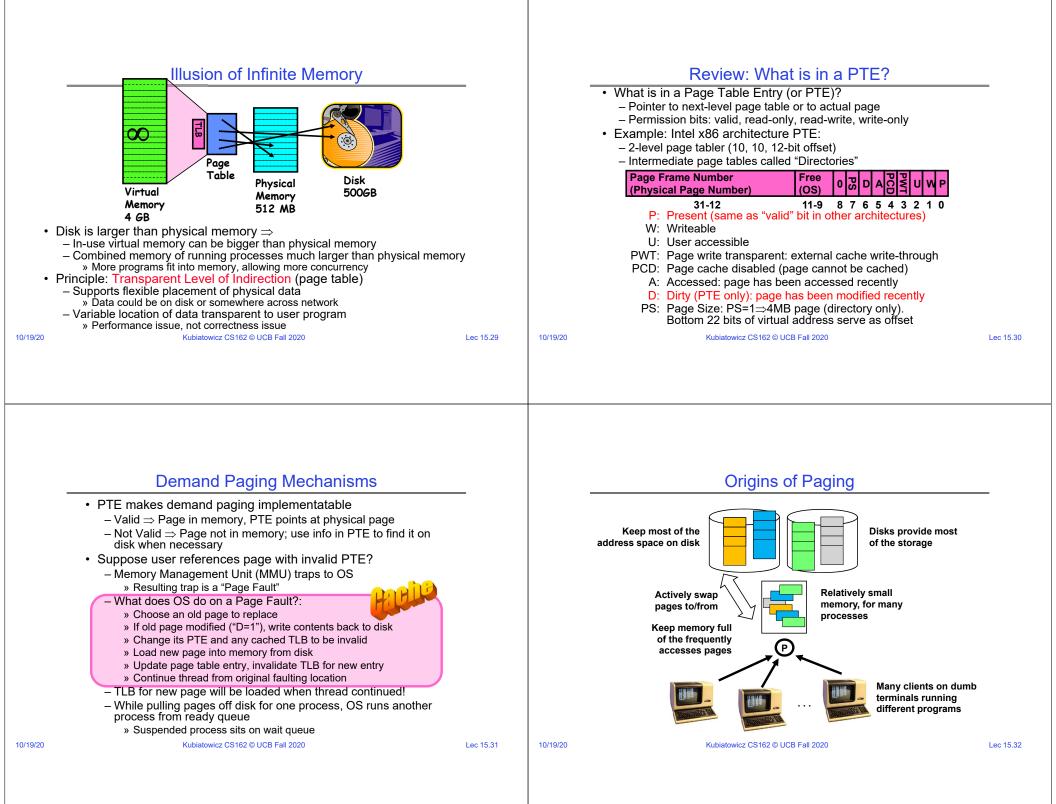

## Many Uses of Virtual Memory and "Demand Paging" ...

- Extend the stack

- Allocate a page and zero it

- Extend the heap (sbrk of old, today mmap)

- Process Fork

- Create a copy of the page table

- Entries refer to parent pages NO-WRITE

- Shared read-only pages remain shared

- Copy page on write

- Exec

- Only bring in parts of the binary in active use

- Do this on demand

- MMAP to explicitly share region (or to access a file as RAM)

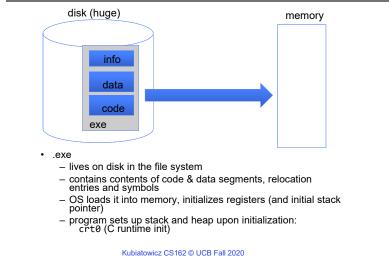

Classic: Loading an executable into memory

Lec 15.35

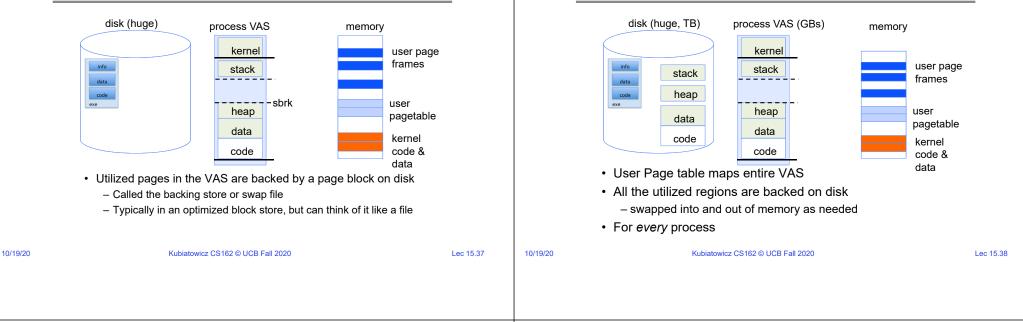

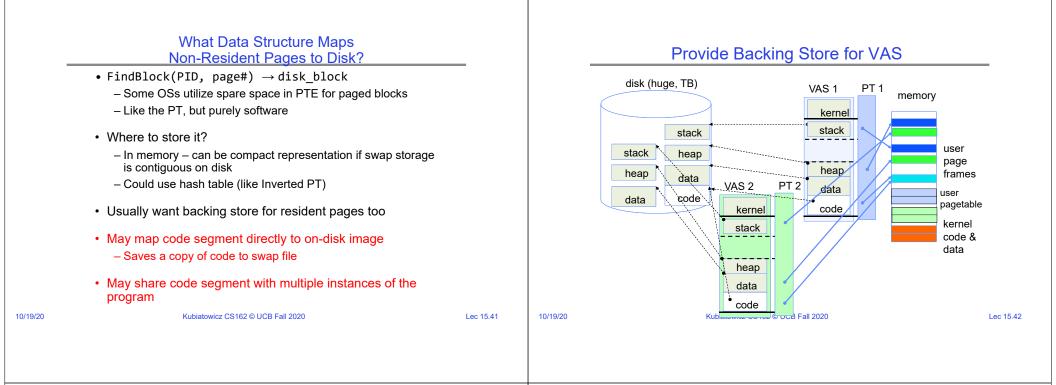

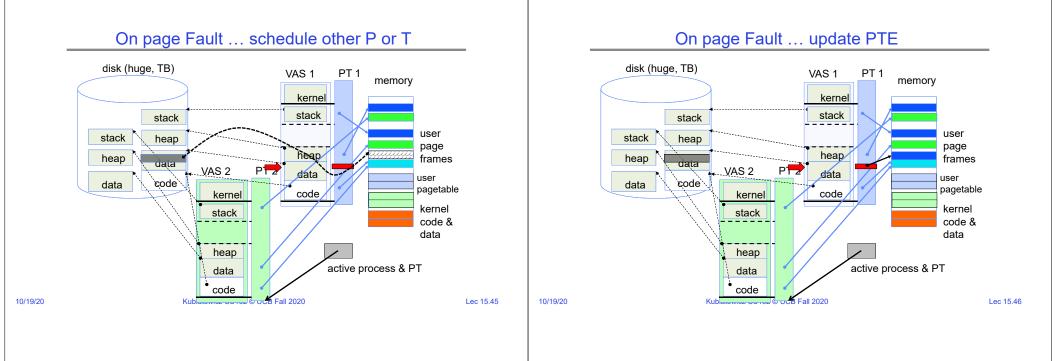

## Create Virtual Address Space of the Process

## Create Virtual Address Space of the Process

- Resident pages to the frame in memory they occupy

10/19/20

- The portion of it that the HW needs to access must be resident in memory

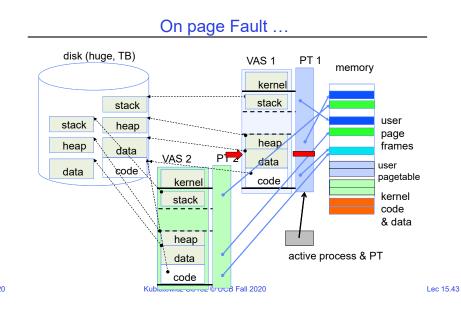

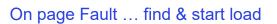

Create Virtual Address Space of the Process

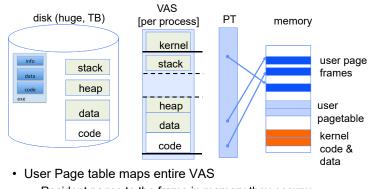

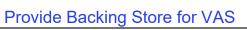

- User Page table maps entire VAS

- · Resident pages mapped to memory frames

- · For all other pages, OS must record where to find them on disk

10/19/20

Fall 2020

active process & PT

Lec 15.47

10/19/20

heap

data

code

Kub

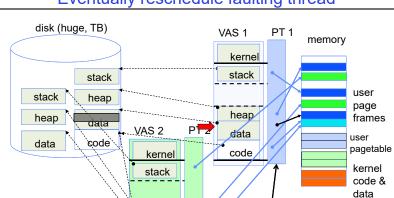

Eventually reschedule faulting thread

Summary: Steps in Handling a Page Fault

Lec 15.48

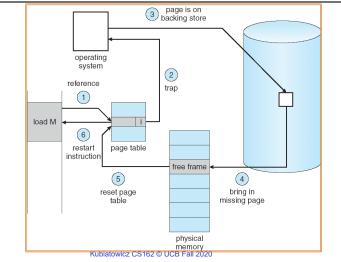

#### Some questions we need to answer! Working Set Model • During a page fault, where does the OS get a free frame? · As a program executes it transitions through a sequence of "working sets" consisting of varying sized subsets of - Keeps a free list the address space - Unix runs a "reaper" if memory gets too full » Schedule dirty pages to be written back on disk » Zero (clean) pages which haven't been accessed in a while - As a last resort, evict a dirty page first Address · How can we organize these mechanisms? - Work on the replacement policy • How many page frames/process? - Like thread scheduling, need to "schedule" memory resources: » Utilization? fairness? priority? - Allocation of disk paging bandwidth Time 10/19/20 Kubiatowicz CS162 © UCB Fall 2020 Lec 15.49 10/19/20 Kubiatowicz CS162 © UCB Fall 2020 Lec 15.50

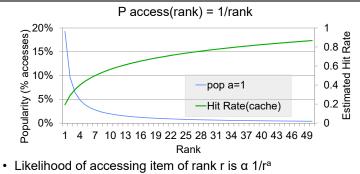

## Cache Behavior under WS model

Another model of Locality: Zipf

- Although rare to access items below the top few, there are so many that it yields a "heavy tailed" distribution

- · Substantial value from even a tiny cache

- · Substantial misses from even a very large cache

10/19/20

## Summary (1/2)

- The Principle of Locality:

- Program likely to access a relatively small portion of the address space at any instant of time.

- » Temporal Locality: Locality in Time

- » Spatial Locality: Locality in Space

- Three (+1) Major Categories of Cache Misses:

- Compulsory Misses: sad facts of life. Example: cold start misses.

- Conflict Misses: increase cache size and/or associativity

- Capacity Misses: increase cache size

- Coherence Misses: Caused by external processors or I/O devices

- · Cache Organizations:

- Direct Mapped: single block per set

- Set associative: more than one block per set

- Fully associative: all entries equivalent

Lec 15.55

10/19/20

Summary (2/2)

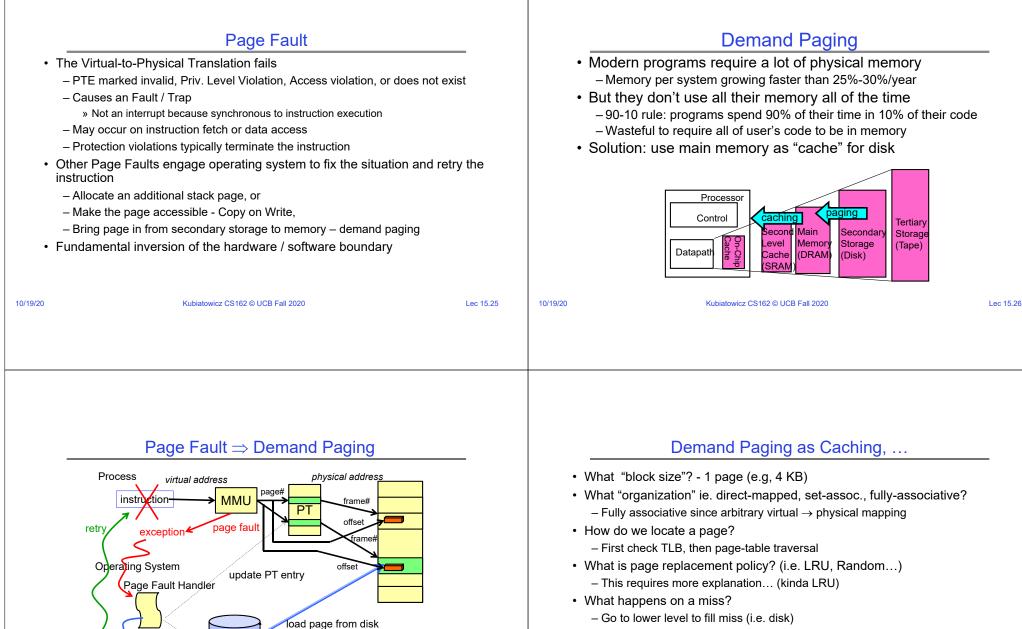

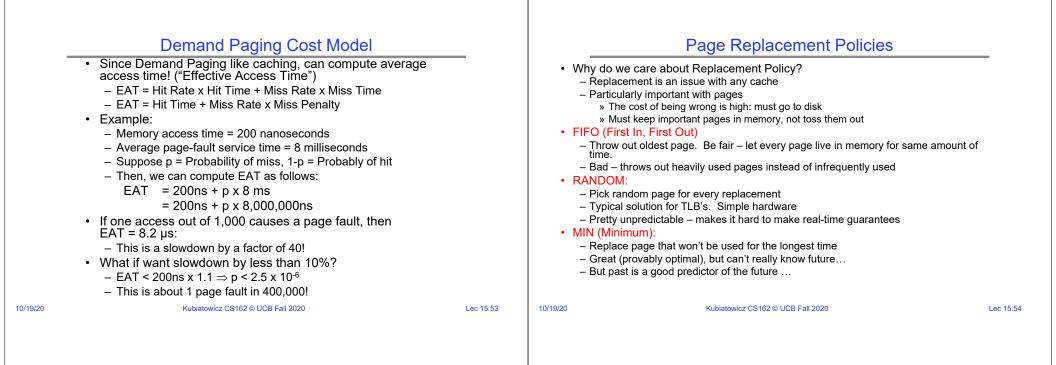

On TLB miss, page table must be traversed and if located PTE is invalid, cause

- Any attempt to access a page that is not in memory generates a page fault,

"Translation Lookaside Buffer" (TLB)

Page Fault

Replacement policies

- Small number of PTEs and optional process IDs (< 512)

- Often Fully Associative (Since conflict misses expensive)

- On change in page table, TLB entries must be invalidated

Demand Paging: Treating the DRAM as a cache on disk

which causes OS to bring missing page into memory

- FIFO: Place pages on queue, replace page at end

- LRU: Replace page used farthest in past

- MIN: Replace page that will be used farthest in future

- Page table tracks which pages are in memory